Board Elex A Graphical Analysis Of A Bjt Amplifier (1) 5q452y

This document was ed by and they confirmed that they have the permission to share it. If you are author or own the copyright of this book, please report to us by using this report form. Report r6l17

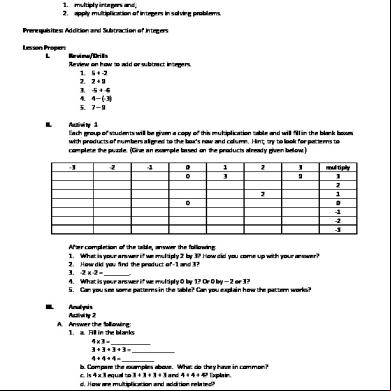

Overview 4q3b3c

& View Board Elex A Graphical Analysis Of A Bjt Amplifier (1) as PDF for free.

More details 26j3b

- Words: 1,534

- Pages: 13

1/2/2017

341482893.doc

1/13

Graphical Analysis of a BJT Amplifier Consider again this simple BJT amplifier:

VCC

We note that for this amplifier, the output voltage is equal to the collector-to-emitter voltage ( vO (t ) vCE (t ) ).

RC

vO (t ) VO vo (t )

iC

RB

vCE

+ _

vi (t )

VBB

If we apply KVL to the collector-emitter leg, we find:

VCC iC RC vCE 0

1/2/2017

341482893.doc

2/13

We can rearrange this to get an expression for the collector current iC in of voltage vCE (i.e., iC f vCE ):

iC

V 1 vCE CC RC RC

Note this is an equation of a line!

iC

y

=

1 RC

vCE m

VCC RC x

b

+

This equation is referred to as the amplifier’s load line, which we can graphically represent as:

y iC b

VCC RC

m

1

RC

x vCE

VCC

1/2/2017

341482893.doc

3/13

The load line provides the circuit relationship (via KVL) between iC and vCE . The value of iC and vCE must lie somewhere along the load line! Exactly where on the load line depends on the device (BJT) relationship between iC and vCE . Recall that this relationship is:

iC active

saturation

The value of iC and vCE must also lie somewhere along this device curve! Q: How can the values for iC and vCE simultaneously be a point on the load line, and a point on the device (BJT) curve? A: Easy! the values for iC and vCE lie at the point where the two curves intersect!

1/2/2017

341482893.doc

4/13

iC VCC RC

iC ,vCE vCE

VCC

Of course, the values of iC and vCE depend on the input to the amplifier: v I (t ) VBB vi (t ) As the voltage v I (t ) changes, so will the values iC and vCE . Note, however, that the load line will not change—the slope 1 RC and y-intercept VCC RC are independent of voltage v I (t ) . What does change is the BJT relationship between iC and vCE . For example, in active mode, the collector current iC is independent of vCE (we’re ignoring the Early effect)! However, the collector current iC of a BJT is dependent on the voltage base-to-emitter vBE .Thus, as v I (t ) changes, so does vBE , resulting in a new BJT relationship (curve) between iC and vCE . Graphically, we can represent this as:

1/2/2017

341482893.doc

5/13

iC v I 3 vI t3 v I 2 v I t2 v I 1 v I t1

vCE where VI 1 , VI 2 , VI 3 are three different input voltages such that VI 1 VI 2 VI 3 . Thus, as the input voltage v I (t ) changes with time, the BJT iC versus vCE curve will change, and its intersection with the amplifier load line will change—iC and vCE will likewise be a function of time! Say that the small-signal input voltage is zero (vo (t ) 0 ). In this case, the input voltage is simply a constant bias voltage ( v I (t ) VBB ). The collector current and voltage collector-toemitter are likewise DC bias values ( IC and VCE ). The intersection of the two curves in this case define the operating point (bias point, Q point) of the amplifier.

1/2/2017

341482893.doc

6/13

iC VCC RC

Q po int

IC

vI VBB

vCE

VCE

VCC

Q: I see! We know that a large DC collector current results in a large transconductance gm—a result that is typically required for large voltage gain. It appears that we should make VBB (and thus IC ) as large as possible, right? A: NO! There is a big problem with making the bias voltage VBB too large—BJT saturation will result ! We can graphically show this unfortunate occurrence:

VCC RC

IC

iC

vI VBB (large!)

saturation VCE 0.2 V

vCE

VCC

1/2/2017

341482893.doc

7/13

A BJT in saturation makes a poor amplifier! Q: Oh I see! We need to set bias voltage VBB to be large, but not so large that we push the BJT into saturation, right?

VCC RC

IC

active VCE 0.7 V

vI VBB (large)

vCE

VCC

A: NO!! There is a big problem with this strategy as well! , it is the total input voltage that will determine the BJT curve. If we DC bias the amplifier so that it is nearly in saturation, then even a small voltage vi can “push” the BJT into saturation mode. For example, recall that the small signal input vi (t ) is an AC signal. In other words its time averaged (i.e., DC ) value is zero, meaning that the value of vi (t ) will effectively be negative half of the time and positive the other half.

1/2/2017

341482893.doc

8/13

Say then that the magnitude of the small signal input is limited to a value vi : vi (t ) vi So that: vi vi (t ) vi

for all time t

and thus:

VBB vi vI (t ) VBB vi

for all time t

Let’s now look at three scenarios for the small-signal input voltage vi : 1) vi vi

2) vi 0

3) vi vi

The resulting output voltage will of course be different for each case:

iC

vI VBB vi

VCC RC

vI VBB vI VBB vi

0.2 VV

CE

vCE

vCE VCE vo

VCC

1/2/2017

341482893.doc

9/13

Look what happened here! If the input small-signal is “large” and positive, the total input voltage ( and thus total vBE) will be too large, and thus push the BJT into saturation. The output voltage in this case (when v I VBB vi ) will simply be equal to:

vO (t ) 0.2 (BJT saturated) as opposed to the ideal value:

vO (t ) VCE vo (BJT active) where vo Avo vi . Note for this amplifier, the small-signal voltage gain Avo is negative, so that the value vo is also negative: vo Avo vi 0 Since the BJT is in saturation during some portion of vi (t ) , the amplifier output signal will not look like the input signal— distortion will result! Q: Now I get it! We need to make VBB small, so that the BJT does not enter saturation, and the output signal is not distorted! A: NO!! There is a problem with this too!

1/2/2017

341482893.doc

10/13

We can again graphically examine what happens if we make the bias voltage VBB too small.

iC VCC RC

vI VBB vi

vI VBB vi v

CE

VCE vo

VCE

vI VBB vCE vCE VCC

Look what happened here! If the input small-signal is “large” and negative, the total input voltage ( and thus total vBE) will be too small, and thus push the BJT into cutoff. Note the collector current will be zero (iC 0 ) when the BJT is in cutoff! The output voltage in this case (i.e., when v I VCE vi ) will simply be equal to:

vO (t ) VCC (BJT cutoff) as opposed to the ideal value:

vO (t ) VCE vo (BJT active)

1/2/2017

341482893.doc

11/13

where vo Avo vi . Note for this amplifier, the small-signal voltage gain is negative, so that the value vo is positive. Since the BJT is in cutoff during some portion of vi (t ) , the amplifier output signal will not look like the input signal— distortion will result! Q: Yikes! Is there nothing we can do to avoid signal distortion? A: To get allow for the largest possible (distortion-free) output signal vo (t ) , we typically need to bias our BJT such that we are about “half way” between biasing the BJT in saturation and biasing the BJT in cutoff. Note if the BJT is in saturation:

iC

VCC RC (BJT saturation)

vCE 0.2 V

1/2/2017

341482893.doc

12/13

Whereas, if it is in cutoff:

iC 0 (BJT cutoff)

vCE VCC

It is evident that for this particular amplifier, biasing “halfway” between saturation and cutoff means biasing such that:

VCE

VCC 2

IC

VCC 2RC

or equivalently:

iC VCC RC VCC

Q po int

2RC

vCE VCE vo

VCE

VCC 2

vI VBB vi

vI VBB vI VBB vi vCE

VCC

vCE VCE vo

The bias solution above is optimal for this particular amplifier design. Other amplifier designs will result in other optimal bias designs—it is up to you determine what they are.

1/2/2017

341482893.doc

13/13

, the total voltage vCE (t ) must be larger than 0.7 V for all time; otherwise saturation (and thus signal distortion will result). Likewise, the total collector current iC (t ) must be greater than zero for all time; other wise cutoff (and thus signal distortion) will result.

341482893.doc

1/13

Graphical Analysis of a BJT Amplifier Consider again this simple BJT amplifier:

VCC

We note that for this amplifier, the output voltage is equal to the collector-to-emitter voltage ( vO (t ) vCE (t ) ).

RC

vO (t ) VO vo (t )

iC

RB

vCE

+ _

vi (t )

VBB

If we apply KVL to the collector-emitter leg, we find:

VCC iC RC vCE 0

1/2/2017

341482893.doc

2/13

We can rearrange this to get an expression for the collector current iC in of voltage vCE (i.e., iC f vCE ):

iC

V 1 vCE CC RC RC

Note this is an equation of a line!

iC

y

=

1 RC

vCE m

VCC RC x

b

+

This equation is referred to as the amplifier’s load line, which we can graphically represent as:

y iC b

VCC RC

m

1

RC

x vCE

VCC

1/2/2017

341482893.doc

3/13

The load line provides the circuit relationship (via KVL) between iC and vCE . The value of iC and vCE must lie somewhere along the load line! Exactly where on the load line depends on the device (BJT) relationship between iC and vCE . Recall that this relationship is:

iC active

saturation

The value of iC and vCE must also lie somewhere along this device curve! Q: How can the values for iC and vCE simultaneously be a point on the load line, and a point on the device (BJT) curve? A: Easy! the values for iC and vCE lie at the point where the two curves intersect!

1/2/2017

341482893.doc

4/13

iC VCC RC

iC ,vCE vCE

VCC

Of course, the values of iC and vCE depend on the input to the amplifier: v I (t ) VBB vi (t ) As the voltage v I (t ) changes, so will the values iC and vCE . Note, however, that the load line will not change—the slope 1 RC and y-intercept VCC RC are independent of voltage v I (t ) . What does change is the BJT relationship between iC and vCE . For example, in active mode, the collector current iC is independent of vCE (we’re ignoring the Early effect)! However, the collector current iC of a BJT is dependent on the voltage base-to-emitter vBE .Thus, as v I (t ) changes, so does vBE , resulting in a new BJT relationship (curve) between iC and vCE . Graphically, we can represent this as:

1/2/2017

341482893.doc

5/13

iC v I 3 vI t3 v I 2 v I t2 v I 1 v I t1

vCE where VI 1 , VI 2 , VI 3 are three different input voltages such that VI 1 VI 2 VI 3 . Thus, as the input voltage v I (t ) changes with time, the BJT iC versus vCE curve will change, and its intersection with the amplifier load line will change—iC and vCE will likewise be a function of time! Say that the small-signal input voltage is zero (vo (t ) 0 ). In this case, the input voltage is simply a constant bias voltage ( v I (t ) VBB ). The collector current and voltage collector-toemitter are likewise DC bias values ( IC and VCE ). The intersection of the two curves in this case define the operating point (bias point, Q point) of the amplifier.

1/2/2017

341482893.doc

6/13

iC VCC RC

Q po int

IC

vI VBB

vCE

VCE

VCC

Q: I see! We know that a large DC collector current results in a large transconductance gm—a result that is typically required for large voltage gain. It appears that we should make VBB (and thus IC ) as large as possible, right? A: NO! There is a big problem with making the bias voltage VBB too large—BJT saturation will result ! We can graphically show this unfortunate occurrence:

VCC RC

IC

iC

vI VBB (large!)

saturation VCE 0.2 V

vCE

VCC

1/2/2017

341482893.doc

7/13

A BJT in saturation makes a poor amplifier! Q: Oh I see! We need to set bias voltage VBB to be large, but not so large that we push the BJT into saturation, right?

VCC RC

IC

active VCE 0.7 V

vI VBB (large)

vCE

VCC

A: NO!! There is a big problem with this strategy as well! , it is the total input voltage that will determine the BJT curve. If we DC bias the amplifier so that it is nearly in saturation, then even a small voltage vi can “push” the BJT into saturation mode. For example, recall that the small signal input vi (t ) is an AC signal. In other words its time averaged (i.e., DC ) value is zero, meaning that the value of vi (t ) will effectively be negative half of the time and positive the other half.

1/2/2017

341482893.doc

8/13

Say then that the magnitude of the small signal input is limited to a value vi : vi (t ) vi So that: vi vi (t ) vi

for all time t

and thus:

VBB vi vI (t ) VBB vi

for all time t

Let’s now look at three scenarios for the small-signal input voltage vi : 1) vi vi

2) vi 0

3) vi vi

The resulting output voltage will of course be different for each case:

iC

vI VBB vi

VCC RC

vI VBB vI VBB vi

0.2 VV

CE

vCE

vCE VCE vo

VCC

1/2/2017

341482893.doc

9/13

Look what happened here! If the input small-signal is “large” and positive, the total input voltage ( and thus total vBE) will be too large, and thus push the BJT into saturation. The output voltage in this case (when v I VBB vi ) will simply be equal to:

vO (t ) 0.2 (BJT saturated) as opposed to the ideal value:

vO (t ) VCE vo (BJT active) where vo Avo vi . Note for this amplifier, the small-signal voltage gain Avo is negative, so that the value vo is also negative: vo Avo vi 0 Since the BJT is in saturation during some portion of vi (t ) , the amplifier output signal will not look like the input signal— distortion will result! Q: Now I get it! We need to make VBB small, so that the BJT does not enter saturation, and the output signal is not distorted! A: NO!! There is a problem with this too!

1/2/2017

341482893.doc

10/13

We can again graphically examine what happens if we make the bias voltage VBB too small.

iC VCC RC

vI VBB vi

vI VBB vi v

CE

VCE vo

VCE

vI VBB vCE vCE VCC

Look what happened here! If the input small-signal is “large” and negative, the total input voltage ( and thus total vBE) will be too small, and thus push the BJT into cutoff. Note the collector current will be zero (iC 0 ) when the BJT is in cutoff! The output voltage in this case (i.e., when v I VCE vi ) will simply be equal to:

vO (t ) VCC (BJT cutoff) as opposed to the ideal value:

vO (t ) VCE vo (BJT active)

1/2/2017

341482893.doc

11/13

where vo Avo vi . Note for this amplifier, the small-signal voltage gain is negative, so that the value vo is positive. Since the BJT is in cutoff during some portion of vi (t ) , the amplifier output signal will not look like the input signal— distortion will result! Q: Yikes! Is there nothing we can do to avoid signal distortion? A: To get allow for the largest possible (distortion-free) output signal vo (t ) , we typically need to bias our BJT such that we are about “half way” between biasing the BJT in saturation and biasing the BJT in cutoff. Note if the BJT is in saturation:

iC

VCC RC (BJT saturation)

vCE 0.2 V

1/2/2017

341482893.doc

12/13

Whereas, if it is in cutoff:

iC 0 (BJT cutoff)

vCE VCC

It is evident that for this particular amplifier, biasing “halfway” between saturation and cutoff means biasing such that:

VCE

VCC 2

IC

VCC 2RC

or equivalently:

iC VCC RC VCC

Q po int

2RC

vCE VCE vo

VCE

VCC 2

vI VBB vi

vI VBB vI VBB vi vCE

VCC

vCE VCE vo

The bias solution above is optimal for this particular amplifier design. Other amplifier designs will result in other optimal bias designs—it is up to you determine what they are.

1/2/2017

341482893.doc

13/13

, the total voltage vCE (t ) must be larger than 0.7 V for all time; otherwise saturation (and thus signal distortion will result). Likewise, the total collector current iC (t ) must be greater than zero for all time; other wise cutoff (and thus signal distortion) will result.